| Figure (3-7) [](https://stanslegacy.com/uploads/images/gallery/2023-12/TUF7LkkiUSFT4h2x-image-1703374861011.png) | Figure (3-8) [](https://stanslegacy.com/uploads/images/gallery/2023-12/pjxVw7assd34zNNX-image-1703374870146.png) |

| Figure (3-9) [](https://stanslegacy.com/uploads/images/gallery/2023-12/eqE5Dz27qkVqIGiU-image-1703374881884.png) | Figure (3-12) [](https://stanslegacy.com/uploads/images/gallery/2023-12/bBte9bH1vjrh9pO1-image-1703374892948.png) |

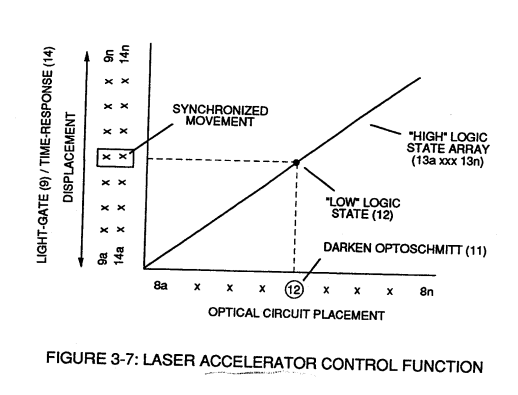

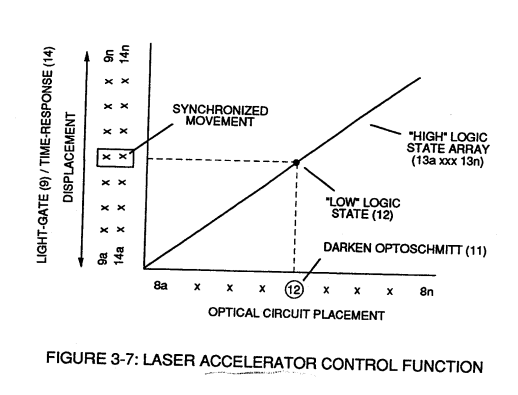

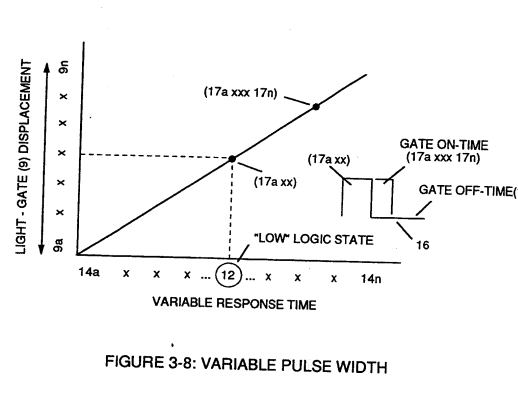

Deflecting (moving) the **light-gate** (9) to **position** (8n) takes longer in **response-time** (14n) than deflecting the light-gate to position (8x) and/or (8xx) or (8xxxx).

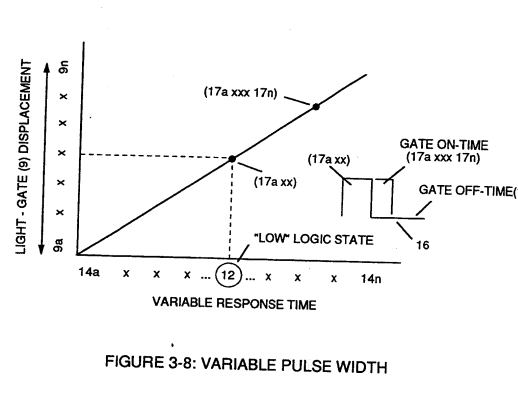

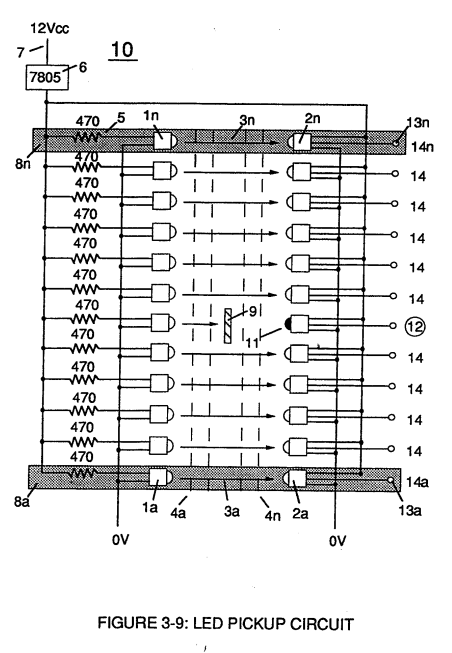

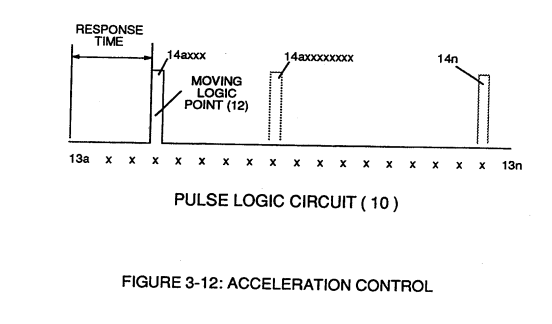

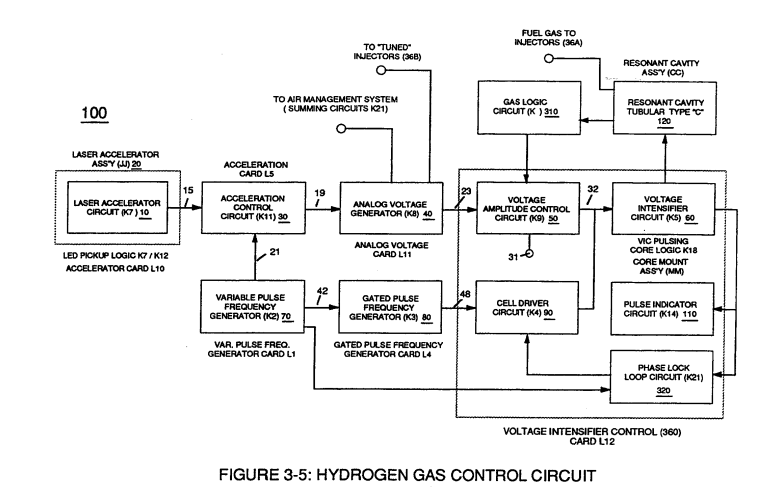

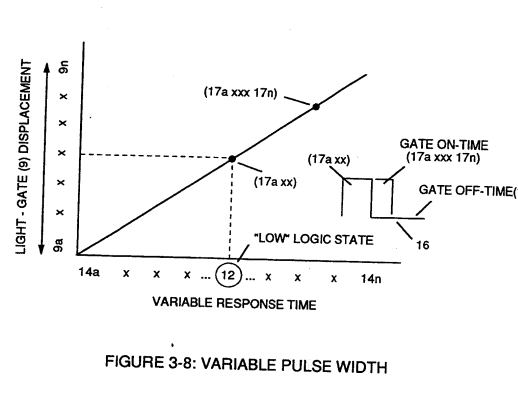

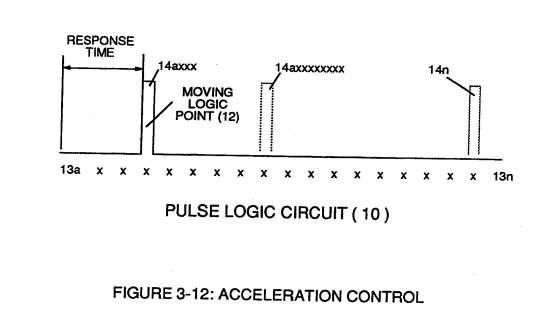

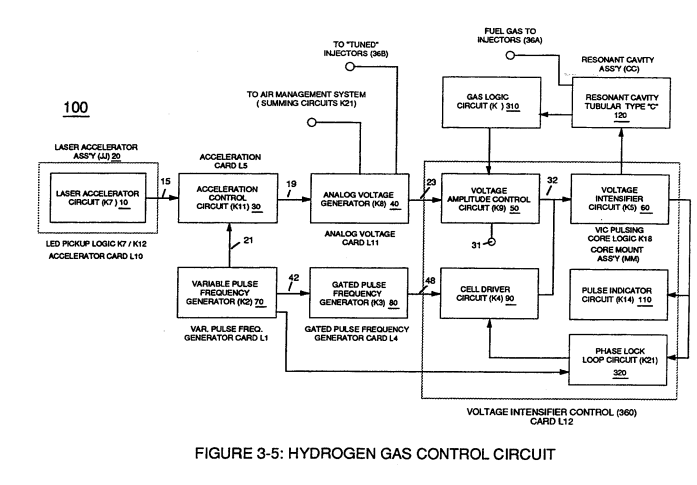

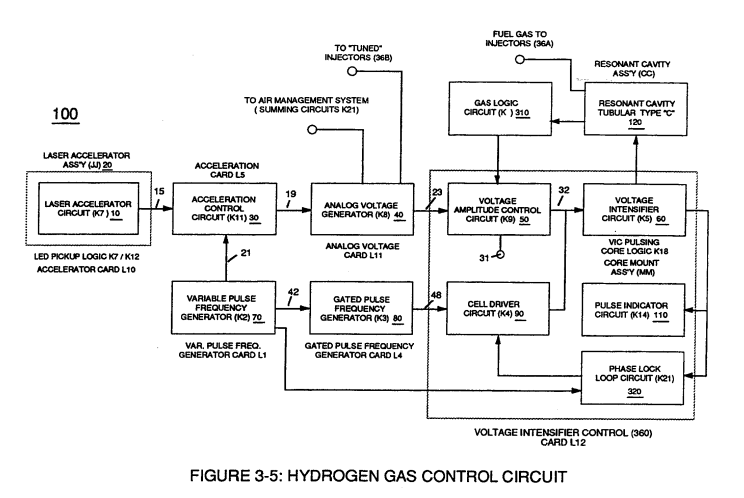

This variable **response-time** (14axx ... 12 ... xxI4n) or **signal output** (15) of Figure (3-5) is, now, electrically transmitted to **Acceleration Control Circuit** (30) of Figure (3-5) since **Laser Accelerator Assembly** (20) of figure (3-10) converts **mechanical displacement** (9a xxx 9n) to **electrical time-response** (14a xxx 14n) of Figure (3-7) by linearly moving (forward and/or reverse direction) "low" **logic state signal** (12) in a array of "high" logic state **output signals** (13a xxx 13n), as further illustrated in Figure (3-8) and Figure (3-12).| Figure (3-7) [](https://stanslegacy.com/uploads/images/gallery/2023-12/TUF7LkkiUSFT4h2x-image-1703374861011.png) | Figure (3-5)[](https://stanslegacy.com/uploads/images/gallery/2023-12/vFSFXV3sntA7ICZs-image-1703375068946.png) |

| Figure (3-8) [](https://stanslegacy.com/uploads/images/gallery/2023-12/pjxVw7assd34zNNX-image-1703374870146.png) | Figure (3-12) [](https://stanslegacy.com/uploads/images/gallery/2023-12/5uNuLwkNkx6jxXkA-image-1703375156797.png) |

Circuit (30) electronically and automatically scans **output signal-array** (14axxx ... 12 ... xx14n) (15) until **circuit** (30) locates, **momentarily registers**, and translates **response-time** (14a xxx ... 12) into a **variable unipolar pulse** (17/18) of Figure (3-8).

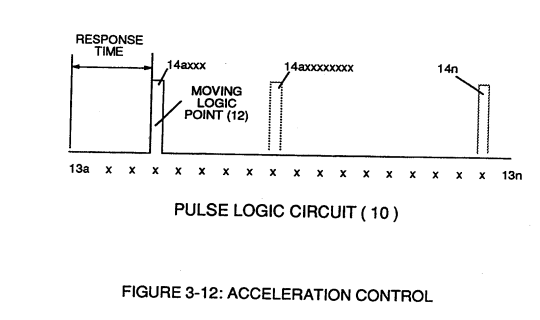

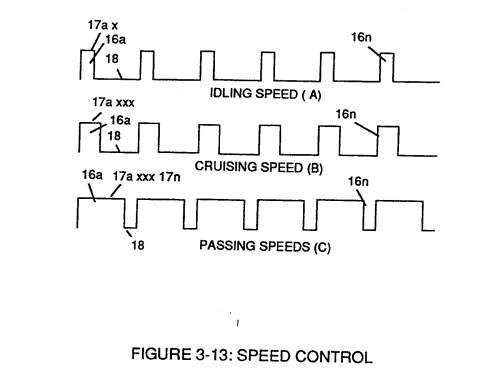

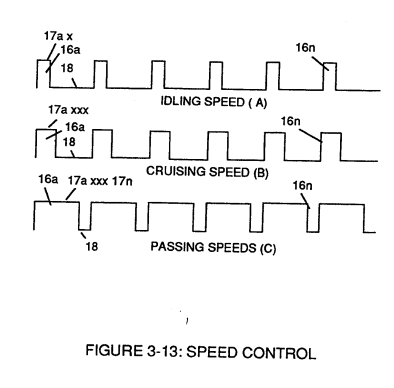

The sweeping action of the **scanning circuit** (30) always starts from **position** (9a) and moves **point** (8ax) to **point** (8axxx) of Figure (3-9) (3-12) until **logic-point** (12) is detected. Once **logic signal** (12) is detected, the sweeping action toggles and recycles back to **start-position** (9a). This toggling (*flip back*) action electronically determines **variable time-response** (14a xxx) regardless of wherever logic point (12) is being momentarily displaced within **circuit array** (13a xxx 13n). **[](https://stanslegacy.com/uploads/images/gallery/2023-12/pjxVw7assd34zNNX-image-1703374870146.png)Toggling action** at full-scale **deflection** (13a xxx 13n) occurs in the range of (10) kHz or above and thus, allows instant response to driver's acceleration demands. **Toggling-time** (scanning-time) is directly synchronized to **light gate** (9) displacement which, in turns, **circuit** (30) further sets up and establishes a given **pulse shape** (16) of Figure (3-8). **Circuit** (30) continues to increase **pulse width** (17axxxx) of Figure (3-8) as the monitored (*detected by < scanning*) **toggling-time** (14a xxxx ... 12) increases when **logic-point** (12) moves farther away from **start-position** (9a) to **stop-position** (9n), as further shown in Figure (3-13) as to Figure (3-12).**Pulse width** (17a xxx 17n) diminishes when **logic-point** (12) reverses direction to start .. **position** (9a).

| Figure (3-12) | Figure (3-13)[](https://stanslegacy.com/uploads/images/gallery/2023-12/BP6hCkX2nps5ADCT-image-1703375624884.png) |

Finally, **circuit** (30) reproduces the **variable controlled pulse-shape** (16) in a continuous **repetitive manner** (16a xxx 16n) of Figure (3-13) and electrically transmits the resultant **pulse-train signal** (19) to **Analog Voltage Circuit** (40), as shown in Figure (3-5).

| Figure (3-13) [](https://stanslegacy.com/uploads/images/gallery/2023-12/kaBCr5103gLcMT1t-image-1703194915396.png) | **Analog Voltage Circuit** (40), as shown in Figure (3-5) [](https://stanslegacy.com/uploads/images/gallery/2023-12/YkkFL3H6bzsH65A5-image-1703194897766.png) |

In retrospect to **engine performance** (*gas pedal attenuation*) (21) of Figure (3-10), a wider **pulse width** (17a xxx) of Figure (3-13C) increases (*accelerates*) engine R.P.M.; whereas, smaller **pulse-width** (17ax) reduces (de-accelerates) engine R.P.M .. Cruising speed (3-13B) of Figure (3-13) is simply accomplished when pulse width remains constant.

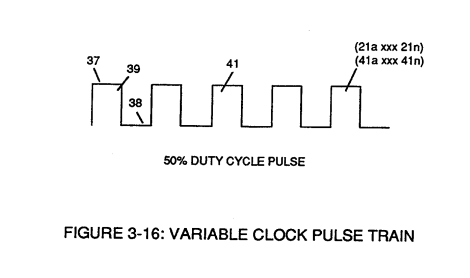

Incoming **clock pulse** (21a xxx 21n) of Figure (3-16) originating from **Pulse Frequency Generator** (70) of| Figure (3-16) [](https://stanslegacy.com/uploads/images/gallery/2023-12/uPM4NAOKxNgpKeiA-image-1703375884091.png) | Figure (3-5) [](https://stanslegacy.com/uploads/images/gallery/2023-12/pkENicyNmypUexcX-image-1703375903506.png) |

The resultant **clock pulse** (21) of Figure (3-16) as to Figure (3-5) is always adjusted to exceed driver's response time to allow for instant acceleration control.